現(xiàn)代計(jì)算機(jī)的核心——中央處理器(CPU),已經(jīng)發(fā)展成為一個(gè)極其復(fù)雜且高效的精密系統(tǒng)。它的工作原理,尤其是多核技術(shù)與緩存層次結(jié)構(gòu)的設(shè)計(jì),深刻體現(xiàn)了計(jì)算機(jī)軟硬件協(xié)同的哲學(xué)。理解這些基礎(chǔ)概念,是洞悉計(jì)算機(jī)系統(tǒng)如何運(yùn)行的關(guān)鍵。

一、從單核到多核:性能提升的范式轉(zhuǎn)變

早期CPU是單核的,即一個(gè)物理處理器只有一個(gè)處理核心,在同一時(shí)間只能執(zhí)行一個(gè)線程的任務(wù)。隨著半導(dǎo)體工藝的進(jìn)步,單純提升單核時(shí)鐘頻率(主頻)遇到了功耗和散熱的天花板。于是,行業(yè)轉(zhuǎn)向了多核架構(gòu)。

現(xiàn)代CPU將兩個(gè)或更多獨(dú)立的處理核心(Core)集成在同一塊芯片上。每個(gè)核心都擁有自己的運(yùn)算單元(ALU)、控制單元和寄存器組,可以獨(dú)立地執(zhí)行指令、處理數(shù)據(jù)。這意味著,在多核CPU上,多個(gè)任務(wù)(或一個(gè)任務(wù)的不同部分)可以真正地并行執(zhí)行,極大提升了系統(tǒng)的整體吞吐量和響應(yīng)能力。

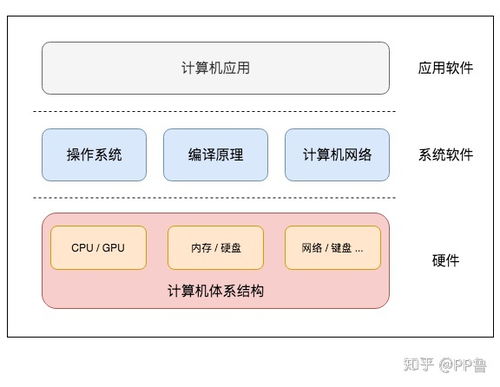

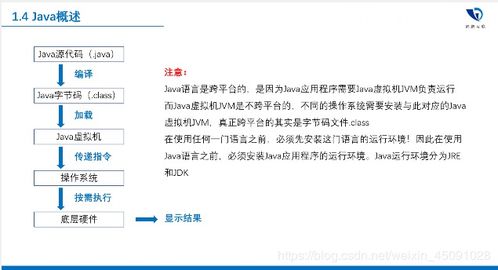

操作系統(tǒng)(軟件層面)的調(diào)度器負(fù)責(zé)將多個(gè)線程或進(jìn)程動(dòng)態(tài)地分配到不同的核心上運(yùn)行,這是軟硬件協(xié)同的經(jīng)典體現(xiàn):硬件提供了并行能力,而軟件(操作系統(tǒng)和應(yīng)用程序)必須通過多線程編程來充分利用這一能力。

二、緩存:彌合速度鴻溝的關(guān)鍵橋梁

CPU核心的運(yùn)算速度極快,而訪問主內(nèi)存(DRAM)的速度相對(duì)慢了幾個(gè)數(shù)量級(jí)。如果CPU每次都需要直接讀寫內(nèi)存,其高速性能將被嚴(yán)重拖累。為了解決這個(gè)“內(nèi)存墻”問題,現(xiàn)代CPU引入了多級(jí)緩存(Cache) 系統(tǒng)。

緩存是一種容量小但速度極快的靜態(tài)存儲(chǔ)器(SRAM),位于CPU核心和主內(nèi)存之間。典型的現(xiàn)代CPU擁有三級(jí)緩存:

- L1緩存:速度最快,容量最小(通常幾十KB),每個(gè)核心獨(dú)享。它又分為指令緩存(L1i)和數(shù)據(jù)緩存(L1d)。

- L2緩存:速度與容量介于L1和L3之間(通常幾百KB),通常也為每個(gè)核心獨(dú)享。

- L3緩存:速度相對(duì)較慢,但容量最大(通常幾MB到幾十MB),由同一芯片上的所有核心共享。

其工作原理基于局部性原理:程序傾向于在短時(shí)間內(nèi)重復(fù)訪問相同的數(shù)據(jù)(時(shí)間局部性)或訪問相鄰的數(shù)據(jù)(空間局部性)。當(dāng)CPU需要讀取數(shù)據(jù)時(shí),它首先檢查L(zhǎng)1緩存,如果找到(命中),則極速獲取;如果未找到(缺失),則依次查找L2、L3緩存,最后才訪問主內(nèi)存。找到的數(shù)據(jù)會(huì)被復(fù)制到更高級(jí)的緩存中,以備下次快速訪問。寫入操作也有復(fù)雜的策略(如寫回、寫通)來保證數(shù)據(jù)一致性。

緩存的存在,使得CPU核心在絕大多數(shù)時(shí)間里都能以接近自身的速度運(yùn)行,有效地隱藏了內(nèi)存延遲。緩存的管理(替換算法、一致性協(xié)議)由硬件自動(dòng)完成,但對(duì)軟件開發(fā)者而言,編寫“緩存友好”的代碼(例如,優(yōu)化數(shù)據(jù)訪問模式)能帶來顯著的性能提升。

三、軟硬件協(xié)同:現(xiàn)代CPU工作的完整圖景

現(xiàn)代CPU的工作絕非僅是核心與緩存的簡(jiǎn)單組合,而是一個(gè)在硬件邏輯與軟件指令驅(qū)動(dòng)下精密協(xié)作的過程:

- 指令流水線與超標(biāo)量:?jiǎn)蝹€(gè)CPU核心內(nèi)部采用流水線技術(shù),將一條指令的執(zhí)行分解為多個(gè)階段(取指、譯碼、執(zhí)行、訪存、寫回),使得多個(gè)指令能像工廠流水線一樣重疊執(zhí)行。更進(jìn)一步,超標(biāo)量架構(gòu)允許一個(gè)核心在一個(gè)時(shí)鐘周期內(nèi)發(fā)射并執(zhí)行多條指令,實(shí)現(xiàn)了指令級(jí)并行。

- 亂序執(zhí)行與分支預(yù)測(cè):為了不讓流水線停滯,CPU會(huì)在指令間不存在依賴關(guān)系時(shí),動(dòng)態(tài)調(diào)整指令的執(zhí)行順序(亂序執(zhí)行),以最大化利用硬件資源。通過分支預(yù)測(cè)單元來猜測(cè)條件跳轉(zhuǎn)指令的走向,并提前執(zhí)行預(yù)測(cè)路徑的指令,大大降低了因程序分支帶來的性能損失。這些復(fù)雜的硬件特性對(duì)軟件是透明的,但程序的規(guī)律性會(huì)影響其效率。

- 硬件與操作系統(tǒng)的協(xié)同:操作系統(tǒng)作為軟件的總管,深度依賴CPU提供的硬件機(jī)制。例如:

- 虛擬內(nèi)存:CPU中的內(nèi)存管理單元(MMU)將程序使用的虛擬地址轉(zhuǎn)換為物理地址,操作系統(tǒng)則管理頁(yè)表,并在頁(yè)面缺失時(shí)處理中斷。

- 中斷與異常:硬件外設(shè)或程序錯(cuò)誤通過中斷信號(hào)通知CPU,CPU會(huì)暫停當(dāng)前工作,轉(zhuǎn)而執(zhí)行操作系統(tǒng)內(nèi)核中的中斷處理程序。

- 特權(quán)級(jí)與系統(tǒng)調(diào)用:CPU提供不同的運(yùn)行權(quán)限級(jí)別(如用戶態(tài)、內(nèi)核態(tài))。當(dāng)應(yīng)用程序需要操作系統(tǒng)服務(wù)(系統(tǒng)調(diào)用)時(shí),會(huì)觸發(fā)一個(gè)特殊的異常,使CPU切換到高特權(quán)級(jí),執(zhí)行內(nèi)核代碼。

- 多核緩存一致性:在多核系統(tǒng)中,每個(gè)核心都有自己的緩存,這可能導(dǎo)致同一數(shù)據(jù)在不同緩存中有不同副本。CPU通過硬件實(shí)現(xiàn)的緩存一致性協(xié)議(如MESI協(xié)議)來確保所有核心看到的內(nèi)存視圖是一致的。當(dāng)某個(gè)核心修改了其緩存中的數(shù)據(jù),協(xié)議會(huì)自動(dòng)通知其他核心,使其緩存中的對(duì)應(yīng)副本失效或更新。

###

現(xiàn)代CPU是一個(gè)以多核并行為宏觀架構(gòu)、以多級(jí)緩存和超標(biāo)量流水線等為微觀優(yōu)化手段的復(fù)雜系統(tǒng)。它的高效工作,離不開硬件自身精妙的設(shè)計(jì),更離不開操作系統(tǒng)和應(yīng)用軟件的緊密配合。從指令集的抽象接口,到緩存一致性協(xié)議的透明維護(hù),再到操作系統(tǒng)調(diào)度器的資源管理,處處彰顯著計(jì)算機(jī)軟硬件協(xié)同設(shè)計(jì)的精髓。理解這些基礎(chǔ),不僅能幫助我們更好地使用計(jì)算機(jī),也是進(jìn)行高性能編程和系統(tǒng)優(yōu)化的基石。